# **European Core Technologies for future connectivity systems and components**

Call/Topic: H2020 ICT-42-2020

Grant Agreement Number: 956830

#### Deliverable

## D3.3 Initial COREnect industry roadmap

**Deliverable type:** Report

WP number and title: WP3 (Roadmap and recommendations)

**Dissemination level:** Public

**Due date:** 30.06.2021

**Document editor:** Björn Debaillie (IMEC)

Section editors: Björn Debaillie (IMEC), Didier BELOT (CEA), Frederic Gianesello (ST),

Gerhard Fettweis (TUD), Jochen Koszescha (IFAG), Marina Plietsch (IFAG), Patrick Cogez (AENEAS), Patrick Pype (NXP), Piet

Wambacq (IMEC), Viktor Razilov (TUD)

Contributing partners: TUD, 5G IA, AENEAS, BOSCH, CEA, EAB, IFAG, IIIV, IMEC, NXP, ST

Internal reviewers: Mohand Achouche (IIIV/Nokia), Matthias Illing (BOSCH)

## **Document History**

| Version | Date       | Author/Editor                                 | Description                   |

|---------|------------|-----------------------------------------------|-------------------------------|

| 0.1     | 19.04.2021 | IMEC                                          | Outline                       |

| 0.2     | 12.05.2021 | All involved partners                         | Initial contributions         |

| 0.3     | 20.05.2021 | All involved partners with support of experts | Advanced contributions        |

| 0.4     | 27.05.2021 | All involved partners with support of experts | Completing most sections      |

| 0.5     | 03.06.2021 | All involved partners with support of experts | Completing most sections      |

| 0.6     | 10.06.2021 | All involved partners with support of experts | Feedback being processed      |

| 0.7     | 17.06.2021 | All involved partners and internal reviewers  | Partial internal review       |

| 0.8     | 29.06.2021 | All involved partners and internal reviewers  | Incorporation internal review |

|         |            |                                               | feedback                      |

| 0.9     | 05.07.2021 | IMEC                                          | Final consolidation           |

| 1.0     | 05.07.2021 | IMEC                                          | Final version (v1.0)          |

## **List of Abbreviations**

| Abbreviation | Denotation                        |  |  |  |

|--------------|-----------------------------------|--|--|--|

| 4G           | 4th generation mobile             |  |  |  |

|              | communication                     |  |  |  |

| 5G           | 5th generation mobile             |  |  |  |

|              | communication                     |  |  |  |

| 6G           | 6th generation mobile             |  |  |  |

|              | communication                     |  |  |  |

| ADAS         | Advanced Driver Assistance        |  |  |  |

|              | Systems                           |  |  |  |

| ADC          | Analog to digital converter       |  |  |  |

| AE           | Antenna elements                  |  |  |  |

| Al           | Artificial Intelligence           |  |  |  |

| API          | Application programming interface |  |  |  |

| ARM          | Advanced RISC machine             |  |  |  |

| ASIC         | Application-specific integrated   |  |  |  |

|              | circuit                           |  |  |  |

| BAW          | Bulk acoustic wave                |  |  |  |

| BiCMOS       | Bipolar CMOS                      |  |  |  |

| CAPEX        | Capital expenditures              |  |  |  |

|              |                                   |  |  |  |

| CAPI         | Common ISDN application           |  |  |  |

|              | programming interface             |  |  |  |

| CCIX         | Cache coherent interconnect       |  |  |  |

| CMOS         | Complementary metal oxide         |  |  |  |

|              | semiconductor                     |  |  |  |

| COVID-19     | Coronavirus disease 2019          |  |  |  |

| CPO          | Co-Packaged Optics                |  |  |  |

| CPU          | Central processing unit           |  |  |  |

| CU           | Central unit                      |  |  |  |

| CXL          | Compute express link              |  |  |  |

| DAC          | Digital to analog converter       |  |  |  |

| DBT          | Dynamic binary translation        |  |  |  |

| DeMUX        | Demultiplexer                     |  |  |  |

| DPLL         | Digital phase locked loop         |  |  |  |

| DPU          | Data processing unit              |  |  |  |

| DSL          | Domain-specific language          |  |  |  |

| DSP          | Digital signal processing         |  |  |  |

| DU           | Distributed unit                  |  |  |  |

| E/O          | Electronics-to-optical            |  |  |  |

| EDA          | Electronic design automation      |  |  |  |

| eDRAM        | Embedded dynamic random-access    |  |  |  |

|              | memory                            |  |  |  |

| EG           | Expert group                      |  |  |  |

| Abbreviation | Denotation                                              |

|--------------|---------------------------------------------------------|

| LoS          | Line of sight                                           |

| LPWAN        | Low power wireless access network                       |

| MANET        | Mobile ad hoc networks                                  |

| MCM          | Multi-chip modules                                      |

| MCU          | Microcontroller unit                                    |

| MEMS         | Micro-electro-mechanical systems                        |

| MIIT         | Ministry of industry and information technology (China) |

| MIMO         | Multiple input multiple output                          |

| ML           | Machine learning                                        |

| MLC          | Multi-level cell                                        |

| mmW          | Millimeter-wave                                         |

| MPSOC        | Multiprocessor system on a chip                         |

| MRAM         | Magneto resistive random-access memory                  |

| MUX          | Multiplexer                                             |

| NB-IoT       | Narrowband IoT                                          |

| NIC          | Network interfce card                                   |

| NVM          | Non-volatile memory                                     |

| O/E          | Optical-to-electronics                                  |

| OS           | Operating system                                        |

| OSI          | Open Systems Interconnection                            |

| OXRAM        | Metal oxide resistive memory                            |

| PA           | Power amplifier                                         |

| PC           | Personal computer                                       |

| PCB          | Printed circuit board                                   |

| PCM          | Phase-change memory                                     |

| PCP          | Programmable computing platforms                        |

| PhD          | Doctor of philosophy                                    |

| PoA          | Power over Air                                          |

| QoE          | Quality of experience                                   |

| QoS          | Quality of service                                      |

| R&I          | Research and innovation                                 |

| RADCOM       | Radar and Communication                                 |

| RAN          | Radio access network                                    |

#### D3.3 Initial COREnect industry roadmap

| EIRP                                  | Effective isotopically radiated       |  |

|---------------------------------------|---------------------------------------|--|

|                                       | power                                 |  |

| eNVM                                  | Embedded non-volatile memory          |  |

| FBAR                                  | Film bulk acoustic resonator          |  |

| FDSOI                                 | Fully depleted silicon on insulator   |  |

| FeFET                                 | Ferroelectric field-effect transistor |  |

| FEM                                   | Front-end module                      |  |

| FinFET                                | Fin field-effect transistor           |  |

| FPGA                                  | Field programmable gate array         |  |

| FW                                    | Firmware                              |  |

| GaN                                   | Gallium nitride                       |  |

| GPU                                   | Graphical processing unit             |  |

| HARQ                                  | Hybrid automatic repeat request       |  |

| h-BN                                  | Hexagonal boron nitride               |  |

| HBT                                   | Heterojunction bipolar transistor     |  |

| HEMT                                  | High-electron-mobility transistor     |  |

| HMI                                   | Human-machine interface               |  |

| HPC                                   | High performance computing            |  |

| HW                                    | Hardware                              |  |

| I/O                                   | Input /output                         |  |

| IC                                    | Integrated circuit                    |  |

| IDM                                   | Integrated device manufacturer        |  |

| IIoT                                  | Industrial internet of things         |  |

| InP                                   | Indium phosphide                      |  |

|                                       |                                       |  |

| IoT                                   | Internet of things                    |  |

| IP                                    | Intellectual property                 |  |

| ISA                                   | Instruction set architecture          |  |

| JEDEC Joint electron device engineeri |                                       |  |

|                                       | council                               |  |

| LDMOS                                 | Planar double diffused MOSFET         |  |

| LNA                                   | Low noise amplifier                   |  |

| RF    | Radio frequency                      |

|-------|--------------------------------------|

| RFID  | Radio-frequency identification       |

| RISC  | Reduced instruction set computer     |

| RTO   | Research and Technology Organization |

| RU    | Radio unit                           |

| SAW   | Surface acoustic wave                |

| SiGe  | Silicon germanium                    |

| SiP   | Systems-in-package                   |

| SME   | Small and medium-sized enterprise    |

| SoC   | System-on-chips                      |

| SoC   | Systems on chip                      |

| SOI   | Silicon on insulator                 |

| SRAM  | Static random-access memory          |

| STDP  | Spike timing dependent plasticity    |

| SW    | Software                             |

| TI    | Tactile Internet                     |

| ToF   | Time of Flight                       |

| TSN   | Time-sensitive networking            |

| TSV   | Through Silicon Via                  |

| TTD   | True-time-delays                     |

| UE    | User Equipment                       |

| ULP   | Ultra-low power                      |

| URLLC | Ultra-reliable low latency           |

|       | communications                       |

| USA   | United States of America             |

| UV    | Ultraviolet lithography              |

| UWB   | Ultra-wideband                       |

| V2X   | Vehicle to everything                |

| VLSI  | Very large-scale integration         |

#### Disclaimer

This document has been prepared by the COREnect project. It reflects the collected views of all experts involved. It does not reflect the opinion of any single COREnect partner or any of the organizations with which the experts are affiliated. The COREnect project and its consortium partners are not liable for any consequence stemming from the reuse of this publication.

## **Table of contents**

| 1.   | Introduction                                                                                                              | 5  |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

| 2.   | Literature overview and highlights                                                                                        |    |

| 3.   | Strategic roadmap: challenges and approach                                                                                | 9  |

| 3.1. | Context and objectives                                                                                                    | 9  |

| 3.2. | Major challenges and opportunities related to future European connectivity system and components                          |    |

| 3.3. | Proposed Industry Roadmap Strategy: How should Europe address future connective technologies with a value-chain approach? | -  |

| 4.   | First draft of strategic industry-relevant R&I roadmaps                                                                   | 17 |

| 4.1. | EG1: compute and store                                                                                                    | 20 |

| 4.2. | EG2: connect and communicate                                                                                              | 31 |

| 4.3. | EG3: sense and power                                                                                                      | 43 |

| 4.4. | Common strategic actions across the expert groups                                                                         | 58 |

| 5.   | Conclusion                                                                                                                | 60 |

| 6.   | References                                                                                                                | 61 |

| 7.   | Appendix                                                                                                                  | 63 |

#### 1. Introduction

One of the key COREnect objectives is to define a strategic R&I roadmap for future European connectivity systems and components, supporting European's strategic autonomy and sovereignty objectives. This roadmap is being defined based on input from all relevant stakeholders across different domains and communities (including SNS and KDT), covering the relevant actors from industry, research, academia, associations, policy analysis etc.

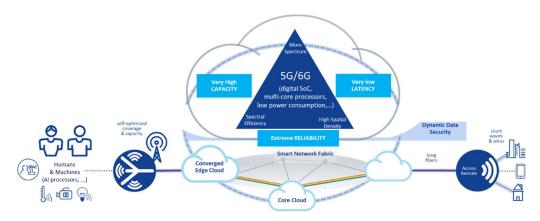

An end-to-end view of future connectivity systems is depicted in Figure 1. To achieve the upcoming needs from emerging applications in e.g., industrial automation, such connectivity systems need offer extreme high capacity, extreme coverage, extreme low latency and high reliability, all at low energy and cost.

Figure 1: COREnect End-to-end System View.

The envisioned roadmap is created over three phases, as illustrated in Figure 2. During the first phase, the roadmap contours are defined, and potential roadmap directions are initially drafted. These roadmap directions are further explored and detailed during the second phase by incremental incorporation of recommendations and feedback. During the third and final phase, the roadmap definition is consolidated. The current deliverable (D3.3) reports the outcome of the first phase and describes the initial COREnect roadmap proposition. The second phase will be concluded with the delivery of D3.4, which will present the intermediate roadmap proposition. The **final** roadmap proposition will be described in D3.6.

Figure 2: COREnect roadmap building timeline.

The text below describes a roadmap with items for the short term, mid-term and long term. Basically, the short and mid-term roadmap banks on growth of existing strengths, while for the long-term items such as establishments of < 2 nm CMOS manufacturing are considered.

The outline of this document is as follows. Section 2 gives an overview of the key publications which act as a reference and baseline for the roadmap activities within COREnect. Section 3 gives an initial glance of the key challenges and possible approaches to define the envisioned strategic roadmap. Section 4 introduces the implemented structure of expert groups and describes the

initial roadmap ideas and potential directions of each expert group. This section is then concluded by the description of possible strategic actions across the different expert groups.

### 2. Literature overview and highlights

Europe is not the only region of the world where roadmaps for electronics components and systems for future networks are derived. Even in Europe, while COREnect is specifically focusing on developing a roadmap of core technologies for future connectivity, relevant roadmapping information can be found in documents issued by other groups, addressing a wider or different but related application scope. Table 1 gives a selected list of those documents.

Table 1: Other relevant roadmapping initiatives.

| Document name                                                                                                     | Related section                               | Date    |

|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------|

| ECS Strategic Research and Innovation Agenda <sup>1</sup>                                                         | Section 2.2 connectivity                      | 01/2021 |

| International Roadmap for Devices and Systems <sup>2</sup>                                                        | Focus team "Outside System Connectivity"      | 2020    |

| 5G ACIA white paper <sup>3</sup>                                                                                  |                                               | 02/2019 |

| Decadal Plan for Semiconductors - SRC <sup>4</sup>                                                                | Chapter 3: New Trajectories for Communication | 01/2021 |

| Webinar "New Apps and New Possibilities: How 5G Will Dramatically Change the Semiconductor Industry" <sup>5</sup> |                                               | 07/2020 |

| "Smart networks in the context of NGI" from<br>NetworldEurope ETP <sup>6</sup>                                    |                                               | 01/2021 |

| NTT DOCOMO White Paper: "5G Evolution and 6G"7                                                                    |                                               | 02/2021 |

In addition to these roadmapping activities, the COREnect consortium could evidence the intensity of the current debate regarding strategic digital autonomy in various regions of the world, translating into legislative actions and/or investment decisions. Below is a brief overview across several countries.

#### Legislative activities in the USA

Responding to concerns, the USA is increasingly reliant on imported microelectronics, Congress enacted the bipartisan Creating Helpful Incentives for Producing Semiconductors (chips) for America Act8 in December as part of the National Defence Authorization Act, its annual defence policy update. The legislation authorizes an array of R&D initiatives as well as a subsidy program for domestic semiconductor manufacturers. However, while early versions of the CHIPS for America Act envisioned spending more than ten billion dollars over five years, the enacted version makes no specific funding recommendations for either the overall initiative or its component elements. In any case, actual funding for them will have to be provided through separate spending legislation.

<sup>8</sup> www.aip.org/sites/default/files/aipcorp/images/fyi/pdf/chips-for-america-act-final.pdf

<sup>&</sup>lt;sup>1</sup> https://aeneas-office.org/pdf/sria-2021/

<sup>&</sup>lt;sup>2</sup> https://irds.ieee.org/editions/2020

<sup>&</sup>lt;sup>3</sup> https://5g-acia.org/wp-content/uploads/2021/04/WP\_5G\_for\_Connected\_Industries\_and\_Automation\_Download\_19.03.19.pdf

<sup>&</sup>lt;sup>4</sup> www.src.org/about/decadal-plan/

<sup>&</sup>lt;sup>5</sup> https://bit.ly/3iXZSyP

<sup>&</sup>lt;sup>6</sup> https://bscw.5g-ppp.eu/pub/bscw.cgi/d392313/Annex%20v2.3%20-%20Public.pdf

www.nttdocomo.co.jp/english/binary/pdf/corporate/technology/whitepaper 6g/DOCOMO 6G White PaperEN v3.0.pdf

On February 24, 2021, the President signed E.O. 14017, directing a whole-of-government approach to assessing vulnerabilities in, and strengthening the resilience of, critical supply chains. This resulted in the release, on June 8, 2021, of findings from this comprehensive 100day supply chain assessments for four critical products: semiconductor manufacturing and advanced packaging; large capacity batteries; critical minerals and materials; and pharmaceuticals and active pharmaceutical ingredients. Of specific interest for the COREnect project are the key findings regarding semiconductor manufacturing and advanced packaging, namely:

- Promote investment, transparency, and collaboration in partnership with industry, to address the current shortage,

- Fully fund the chips for America provisions to promote long-term US leadership,

- Strengthen the domestic semiconductor manufacturing ecosystem,

- Support SMEs and disadvantaged firms along the supply chain to enhance innovation,

- Build a talent pipeline,

- Work with allies and partners to build resilience,

- Protect the US technological advantage.

In particular, the report states that "as an initial step, Congress should fund the chips provisions with at least \$50 billion in funding". Details can be found in the document entitled 100-day supply-chain review report9.

To decrease their dependency on foreign-based semiconductor production, the USA is also attracting foreign investment. A case in point is the Taiwanese company TSMC which broke ground in June 2021 on its \$12 billion semiconductor fab in Arizona<sup>10</sup>. Likewise, Samsung Foundry has filed documents with authorities in Arizona, New York, and Texas seeking to build a leading-edge semiconductor manufacturing facility in the USA. The potential fab near Austin, Texas, is expected to cost over \$17 billion and to create 1,800 jobs<sup>11</sup>.

Finally, the USA is actively using export control laws to prevent mainland China from developing sub-10 nm node technology, for example by barring ASML to sell Extreme UV equipment to Chinese semiconductor manufacturers, and even trying to extend that ban to older, Deep UV equipment<sup>12</sup>.

#### **Mainland China**

In 2015, mainland China released its "Made in China 2025" initiative, which included the ambitious goal of reaching 70 per cent self-sufficiency goal for semiconductor production. However, they are so far falling very short of being on a trajectory meeting that target: IC production in China, including output by both foreign and domestic players, only accounted for 15.7% of its \$125 billion chip market in 2019. If only companies with headquarters in China are considered, their production accounted for just 6.1% of China's total IC market that year. At its current pace China will only achieve one third of its goal.

<sup>12</sup> https://www.techzine.eu/news/infrastructure/56766/usa-tries-to-prevent-all-export-of-asml-machines-to-china/

<sup>9</sup> https://www.whitehouse.gov/wp-content/uploads/2021/06/100-day-supply-chain-review-report.pdf

<sup>10</sup> https://www.datacenterdynamics.com/en/news/tsmc-starts-work-on-12bn-arizona-semiconductor-fab-gets-funding-forjapanese-chip-rd/

<sup>&</sup>lt;sup>11</sup> https://www.anandtech.com/show/16483/samsung-in-the-usa-a-17-billion-usd-fab-by-late-2023

Nevertheless, mainland China main semiconductor manufacturer, SMIC, has been increasing its R&D expenditures rather rapidly in recent years. In 2014, the company spent \$189.7 million, or 9.5% of revenue, on research and development. Five years later, in 2019, the company spent \$629 million, or 20.7% of revenue on R&D. In parallel, its CAPEX was expected to reach \$4.3 billion in 202013. On March 2021, SMIC announced 2020 sales of \$3.9 billion and gross profit of \$0.9 billion, while the debt-to-equity ratio "remained low"14. A large CAPEX can only be achieved via capital injection from the shareholders. Since by late 2018 the Chinese government controlled at least 46.36% of the company, this corresponds to a significant amount of public support.

#### <u>Japan</u>

Similar to the USA, Japan is also discussing with TSMC towards the building of a chip fab in Kumamoto, which would be TSMC first Japanese semiconductor factory<sup>15</sup>.

#### South Korea

Finally, the South Korean government announced on May 13<sup>th</sup>, 2021, a plan by companies to invest 510 trillion won (\$451 billion) throughout 2030 and beefed-up tax benefits to boost chipmakers' competitiveness amid a critical global shortage of the key components. "Our government will unite with companies to form a semiconductor powerhouse. We will support companies concretely." said President Moon Jae-in<sup>16</sup>.

As part of the effort, the Finance Ministry said it will raise the tax deduction ratio for semiconductor research and development investments by big companies to 40% from the current 30%, paving the way for Samsung and SK Hynix to benefit from the eased financial burden. The chipmakers also will enjoy higher deductions for investments in facilities, as the government is doubling that ratio to 6%, the ministry said.

<sup>&</sup>lt;sup>16</sup> https://asia.nikkei.com/Business/Tech/Semiconductors/South-Korea-plans-to-invest-450bn-to-become-chip-powerhouse

8

<sup>13</sup> https://www.eetimes.com/smic-advanced-process-technologies-and-govt-funding-part-2

<sup>&</sup>lt;sup>14</sup> https://www.smics.com/en/site/news\_read/7809

<sup>&</sup>lt;sup>15</sup> https://www.datacenterdynamics.com/en/news/tsmc-considers-chip-fab-in-kumamoto-its-first-japanese-semiconductorfactory/

## 3. Strategic roadmap: challenges and approach

#### 3.1. Context and objectives

Considering the full value chain, COREnect's main objective is to:

Develop a high-level strategic roadmap of core technologies for future connectivity systems and components, targeting the next generation European telecommunications networks and services (5G and beyond).

This roadmap proposal is being developed while considering the following factors:

- The end goal of this industrial strategy is to support Europe's twin transition towards

a green and digital future: enabling our society to embrace digitalization in a sustainable

way (from cost and power efficiency point of view) is a key societal challenge.

- The necessity to strengthen Europe's strategy to differentiate and lead in its most important value chains while enabling the European ecosystem to adapt to a profound on-going value chain transformation: it is mandatory to continue to innovate on "more than Moore" technologies to maintain Europe's leading role on key verticals. Today, advanced connectivity solution does not necessarily need chips processed in ≤ 5 nm node, but they will do so in the future. Moreover, the European ecosystem must also adapt to the value chain transformation induced by digitalization which requires to develop the relevant skills and technologies.

- Aim for a realistic strategy keeping in mind that available economical resources are limited: connectivity systems require a broad range of technologies which cannot be completely mastered by a single geographic area. This implies to clearly define key priorities in agreement with existing strengths.

- The societal impact of the COVID-19 pandemic: the current pandemic has underlined the importance of connectivity infrastructure in the resilience of our society.

- The COVID-19 pandemic impact on key technologies supply chain and importance to secure Europe's sovereignty (which does not mean autarky but allows for own decisions in Europe): the current supply chain issues underline the importance of cooperation with like-minded partners to support open, fair and rules-based trade to reduce strategic dependencies.

- The geopolitical trade tensions between the USA and China: the export regulations on USA technologies have contributed to disruptions in the current supply chains. Moreover, Europe's current dependency on USA technologies hampers Europe to act independently and to take strong standpoints on business-related sovereignty topics.

- The objective of the European Commission to enable Europe to produce 20% of the world's semiconductors by 2030 to meet future industry demand: to secure European sovereignty, manufacturing of semiconductors in Europe should reflect the relative size of its domestic market and the strength of its industrial players on key verticals.

- The necessity to reduce Europe's dependence on USA for EDA solutions, software and

IP required to develop future connectivity systems: the increased trade tensions

between the USA and China highlighted Europe's vulnerability to USA technology; it

indicated alarming sovereignty issues on connectivity technologies if extraterritorial

rules are applied to European semiconductor players.

- The necessity to bridge the current gap on advanced processor design to secure

Europe's industrial strategy and digital sovereignty: advanced computing is key to

support the digitalization of our society. Today, Europe heavily relies on USA advanced

computing technologies. This causes a critical dependency and might impact Europe's

key ambition for open, ethical, trustworthy, and explainable AI and computing.

The European Commission's objective to enable a fabrication plant to produce leading edge technology (2 nm or even beyond) through selected partnerships to ensure security of supply, in the next 10 to 15 years: due to the importance of leading-edge semiconductor technologies to manufacture advanced computing chips, Europe has a role to play to enable a more diverse and consequently resilient supply chain to reduce its critical dependencies, while remaining open. It is quite likely that the advent of 6G will fire up the semiconductor market and its entire ecosystem. This is a strategic consideration but any decision on installing advanced CMOS manufacturing in Europe will need a detailed predictive market study.

Keeping in mind the previous context and objectives, we first propose a synthesis of the current position of Europe on the connectivity market to identify opportunities and gaps. We will then propose a global industry roadmap strategy which will be finally derived in concrete actions proposed by COREnect's expert groups.

## 3.2. Major challenges and opportunities related to future European connectivity systems and components

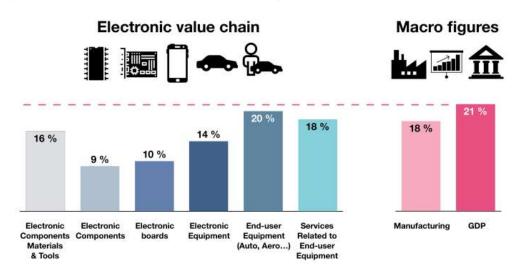

To identify Europe's major challenges or opportunities concerning connectivity technology, we start the discussion by a review of Europe's position in the overall value chain. As illustrated in Figure 3, Europe still holds a good share in materials and tools to produce electronic components. Europe's production share is, however, lower at levels such as electronic equipment, electronic boards, and electronic components.

Figure 3: European share of the world production of the global electronic value chain [Dec20].

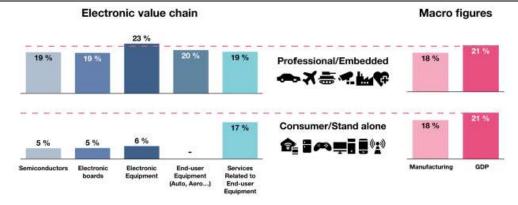

In Europe, the leading end-user segments are industrial electronics, aerospace defense and security, and automotive electronics. In the global electronics ecosystem, the leading segments are still the consumer mass markets (mobile phones, PCs). Consequently, Europe's share in the world production is also highest in those segments where Europe is strongest, as illustrated in Figure 4.

Figure 4: European share of the world production of the global focusing on professional/embedded and consumer electronic value chains [Dec20].

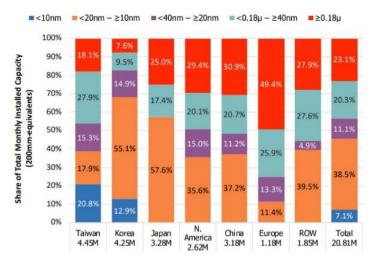

While Europe is just producing 9% of the overall electronic components (see Figure 3), its market share is 19% on the market it serves today (professional and embedded segments, the wireless infrastructure market being a good example with Ericsson and Nokia). This figure is in line with Europe's GDP. Since Europe hardly addresses the consumer market, the European ecosystem requires a moderated manufacturing capacity mainly focused on mature or derivate technology. For example: automotive represents today only about 10%, but this is expected to increase in the coming years. The installed European semiconductor manufacturing capability to address Europe's key verticals is sized accordingly. As illustrated in Figure 5, Europe has a strong presence on 200 mm facilities (with STMicroelectronics and Infineon among the top 5 leaders) which is in line with the technologies required by the European ecosystem and value chain.

(Ranked by Share of Total WW Monthly Installed Capacity)

| 300mm Wafers |                    |                       | 200mm Wafers |                    |                       | ≤150mm Wafers |                    |                       |

|--------------|--------------------|-----------------------|--------------|--------------------|-----------------------|---------------|--------------------|-----------------------|

| WW<br>Share  | Top 10<br>Relative | Top 10 in<br>Capacity | WW<br>Share  | Top 10<br>Relative | Top 10 in<br>Capacity | WW<br>Share   | Top 10<br>Relative | Top 10 in<br>Capacity |

| 21%          |                    | Samsung               | 10%          |                    | TSMC                  | 9%            |                    | CR Micro              |

| 15%          |                    | TSMC                  | 6%           |                    | STMicro               | 8%            |                    | Silan                 |

| 14%          |                    | Micron                | 6%           |                    | UMC                   | 8%            |                    | Nuvoton               |

| 13%          |                    | SK Hynix              | 6%           |                    | Infineon              | 7%            |                    | ON Semi               |

| 11%          |                    | Kioxia/WD             | 6%           |                    | TI                    | 5%            |                    | STMicro               |

| 6%           |                    | Intel                 | 5%           |                    | SMIC                  | 4%            |                    | TI                    |

| 4%           |                    | GlobalFoundries       | 4%           |                    | Vanguard              | 3%            |                    | Rohm + Lapis          |

| 3%           |                    | UMC                   | 4%           |                    | NXP                   | 3%            |                    | Toshiba               |

| 2%           |                    | Powerchip             | 4%           |                    | ON Semi               | 3%            |                    | Diodes                |

| 2%           |                    | TI                    | 3%           |                    | Toshiba               | 3%            |                    | TSMC                  |

WW Share is each company's share of total industry capacity for that wafer size.

Blue bars indicate the relative amount of capacity held by each company among the top 10 leaders.

Note: Includes shares of capacity from joint ventures.

Source: IC Insights

Figure 5: Installed capacity leaders in December 2020 by wafer size [EMS21].

The situation on 300 mm wafers manufacturing is completely different. On 300 mm, there is no European actor among the top 10 players. This is directly correlated with the European position on the market since the top 300 mm manufacturing players are addressing either memory (Samsung, Micron, SK Hynix, Kioxia) or advanced logic (Samsung, TSMC, Intel). These are two areas where Europe is hardly represented. As illustrated in Figure 6, the installed manufacturing

capability of a given region directly correlates with the technology nodes required by the targeted markets of the associated value chain and ecosystem.

Figure 6: Monthly installed capacity for each geographic region in December 2020 [Nen21]. "ROW" means "rest of the world".

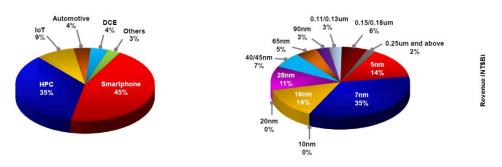

China, Japan, USA, and Korea have most of their installed capacity for technology ranging from > 10 nm to < 20 nm, which serves their memory production. On the other hand, 75% of Europe's installed capacity supports > 40 nm (50% for technologies > 180 nm) which serves its key verticals (automotive, industrial, health, ...). Taiwan has a more balanced situation because TSMC's foundry business model clearly focusses on the most advanced nodes. TSMC's 1Q21 revenue, depicted in Figure 7, shows that the smaller nodes are driven by the smartphone and HPC business.

## 1Q21 Revenue by Platform 1Q21 Revenue by Technology

Figure 7: TSMC's 1Q21 revenue split per application and technology [TSM21].

We can also note that, while 7 nm and 5 nm represent 20% of TSMC's capacity, they generate ~50% of the revenue. This point is the foundation of TSMC's high-end foundry business positioning: by maintaining its leadership on advanced nodes and being the first to deliver volume manufacturing, it captures most part of the market value. This enables them to support the high CAPEX required to develop the next nodes and install the necessary capacity (TSMC's CAPEX in 2021 is set to 30 B\$). Consequently, even a company able to offer equivalent

technology and spending a large CAPEX such as SAMSUNG is today having a hard time to keep up with TSMC. From pure manufacturing side, the entry barrier is high and at short term, it may prove difficult for anyone to dispute the leadership of TSMC. Moreover, advanced manufacturing capability of 7 nm or beyond needs to come with a complex ecosystem that cannot be deployed on a very short term. Indeed, new Fab players will have to build first the design enablement ecosystem (IPs, CAD flow, ...) and prove to be a reliable partner able to deliver targeted performances in large volumes and in time.

While Huawei used to be TSMC's second largest customer just after Apple, the USA export restrictions have reshaped the landscape. Today, most TSMC key customers for 7 nm and 5 nm technologies are USA fabless companies. The only exceptions are Samsung and MediaTek. It illustrates a key weakness of the European fabless ecosystem. Since there are currently no large European fabless or system companies requiring high volumes in extremely scaled semiconductor technologies (<7 nm node), the current industrial drive to develop such manufacturing capabilities shows to be rather limited. Moreover, given that China and USA are today leading in strategic topics such as AI, they are not expected to own the required manufacturing capability. As such, they are as dependent on the Taiwanese semiconductor technology as Europe.

However, the lack of < 20 nm node manufacturing capability in Europe does not mean that Europe refrains from this topic. Europe's strong position on semiconductor manufacturing equipment enables Europe to play a strategic role on the value chain. ASML is a good example since it is today the sole source of EUV lithographic scanner on the market. Figure 8 shows the EUV shipment forecast by customer and learns how leading foundries such as TSMC, Samsung and Intel are relying today on ASML (and consequently on European technology). This is a strong pledge for Europe.

| ^                   | EUV shipments (unit) |      |      |       |       |       |  |

|---------------------|----------------------|------|------|-------|-------|-------|--|

| Company             | 2018                 | 2019 | 2020 | 2021E | 2022E | 2023E |  |

| TSMC                | 7                    | 16   | 18   | 28    | 31    | 33    |  |

| Samsung             | 3                    | 5    | 8    | 9     | 14    | 15    |  |

| Intel               | 4                    | 3    | 3    | 2     | 3     | 5     |  |

| GlobalFoundries     | 1                    | 0    | 0    | 0     | 0     | 0     |  |

| Hynix               | 1                    | 1    | 1    | 1     | 1     | 1     |  |

| Micron              | 0                    | 0    | 0    | 1     | 1     | 1     |  |

| SMIC                | 0                    | 0    | 0    | 0     | 0     | 0     |  |

| Others              | 2                    | 1    | 1    | 0     | 0     | 0     |  |

| Total EUV shipments | 18                   | 26   | 31   | 41    | 50    | 55    |  |

| EUV ASP (EUR mn)    | 105                  | 109  | 145  | 145   | 153   | 163   |  |

Source: Mizuho Securities Equity Research Estimates

Figure 8: ASML EUV shipment forecast by customer.

The recent USA export restriction prevented Chinese companies to access to < 14 nm nodes by preventing USA vendors (such Applied Material, KLA, ...) and foundries to sell their USAtechnology based products. This provides interesting perspectives concerning the position that Europe can adopt to safeguard its sovereignty and access to key technologies related to connectivity.

Consequently, even if Europe does not own today the complete connectivity value chain, it still has a leading position on key topics. These topics include semiconductor manufacturing equipment, manufacturing of differentiated technologies, leading position on the wireless

infrastructure market, ... This enables Europe to play a leading role in future connectivity technology development and secure its sovereignty by strengthening its partnership with other countries.

Worth mentioning is the leadership gained by the European RTOs in semiconductor science and engineering to seed the innovations in design architectures and manufacturing technologies. With the support of European funds incentives, basic research is stimulating and attracting industry R&D since their respective contributions are complimentary and not redundant. For example, the FinFET transistor architecture, which has replaced the classical planar architecture in the recent CMOS generations, is the result of several decades of R&D collaborations. Similarly, the technology used by ASML for its flagship EUV lithography started in the 1980s on the use of soft x-rays.

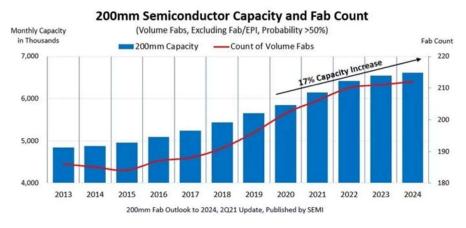

Moreover, from pure manufacturing point of view, the importance of leading-edge technology nodes versus legacy ones must be put into perspective. Figure 9 shows that the capacity in leading edge technology nodes will grow strongly in the coming 3 years while the legacy nodes will still represent a significant portion of the overall capacity (but also growing in absolute numbers).

#### Forecast Monthly Installed Capacity Shares - by Min. Geom. <20nm - ≥10nm <40nm - ≥20nm <0.18µ - ≥40nm ≥0.18µ</p> 100% 18.6% 90% 19.8% 19.0% 20.6% 23.7% 22.1% Share of Monthly Capacity as of December 80% 18.5% 18.3% 18.4% 70% 18.6% (200mm-equivalents) 18.7% 19.8% 60% 6.7% 9.4% 10.8% 50% 13.4% 26.2% 28.6% 40% 31.3% 35.5% 30% 38.4% 38.8% 20% 29.9% 26.9% 22.6% 10% 16.0% 10.0% 0% Dec-22F Dec-19 Dec-20F Dec-21F Dec-23F Dec-24F 19.51M 21.09M 22.92M 24.08M 25.15M 25.99M Source: IC Insights

Figure 9: Wafer Capacity by Feature Size Shows [ICi20].

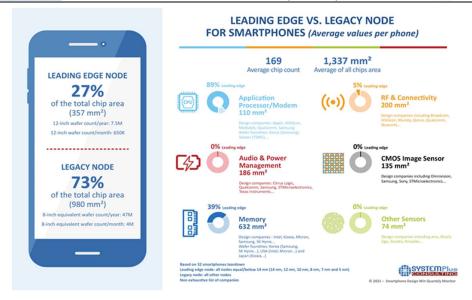

The growing trend of leading-edge technology capacity is mainly driven by consumer products such as smartphones. As illustrated in Figure 10, leading-edge technologies are used in 89 % of the smartphone's application processor and modem, whereas only 5% of the RF and connectivity chips use such technologies. Consequently, in the smartphone market, leading edge nodes represent 27% of the overall chip area (~7.5M 12" wafer count/year) while legacy nodes are addressing the remaining 73% (~47M 8" wafer count/year).

Figure 10: Leading edge versus legacy technology nodes used in smartphones [Sys21].

Given this persisting strong demand, the legacy technology node market will remain very active in the foreseeable future. The associated 200 mm installed capacity is expected to increase to record levels from 2020 to 2024, beating the last records seen in 2006 and 2007 (as illustrated in Figure 11). Moreover, one should also remember that European legacy technology node players are also transitioning to 300 mm fabs to increase even further installed capacity. Infineon's new 300 mm Fab in Villach in Austria, STMicroelectronics' new 300 mm fabs in Agrate in Italy, Bosch's new 300 mm facility in Dresden in Germany and STMicroelectronics' 300 mm fab extension in Crolles in France are good examples of such actions.

Figure 11: 200 mm semiconductor capacity and count of fabs [Fas21].

Put more simply, there is no opposition to be made between leading edge and legacy technology nodes. Strengthening key partnerships within Europe may secure the technology access and the European sovereignty. Still, not owning the complete technology portfolio does not prevent Europe to capture a significant part of the semiconductor manufacturing chain. Europe's developed technologies and associated installed might, however, remain closely linked to needs of Europe's key verticals and the European overall position in the value chain. Having such

technology and processing capacity, however, is likely to stimulate existing and to initiate new ecosystems in Europe.

## 3.3. Proposed Industry Roadmap Strategy: How should Europe address future connectivity technologies with a value-chain approach?

Based on the previous section, we can summarize European challenges and opportunities on connectivity technology to support its strategic agenda as follows:

#### **Opportunities:**

- Strong global position on wireless and wireline infrastructure markets and R&D

- Strategic link between core semiconductor technology capability and key verticals (automotive, industrial, space and defense, ...)

- Combining those two assets makes Europe a strong contender to take a leading role towards 6G and beyond, while covering the entire value chain

- Europe has strong research in heterogeneous integration for many applications (highperformance computing, photonics, RF)

- In the industrial data market, that is several orders of magnitude bigger than the personal data market, Europe should not leave the storage and handling of these data (both 'central' and 'edge') to non-European companies.

#### Challenges:

- Digitalization modifies the European value chain, in which Europe risks to reduce its technological sovereignty. The rise of AI, for example, is likely to increase our dependency on USA technologies.

- Geopolitical tensions and trade restrictions impose an increased risk of disruption of the European supply chain. It is key for Europe to mitigate this risk through a more diverse and resilient supply chain.

With financial resources being limited, COREnect is proposing an industry roadmap with a 10to 15-year timeline. This roadmap addresses different timeframes with a changing focus in terms of strategic investments, markets, and technological development.

#### **Short term (2 years from now):**

- Strengthen areas where Europe is leading (BiCMOS, III-V, RF, analog, mixed signal, photonics ...) to secure its position and gain market share to ensure Europe to play a leading role for 6G: Europe needs to continue to innovate on differentiated technologies where it leads today to secure its leadership. Transitioning from 200 mm to 300 mm fab manufacturing differentiated technologies is a key industrial challenge.

- Secure access to < 7 nm CMOS technology: Digitalization requires the know-how to design dedicated advanced computing chips. Europe needs to secure both the design capability as well as the access to a diverse and trustworthy supply chain.

- Strengthen the education on IC design (both in analog/RF and digital): To enable an appropriate pool of experts able to address European industrial players' needs but also make Europe an appealing place to invest. Contribute on open-source initiatives in processor core design IP (RISC-V) to differentiate on what today is openly available.

- Enable Europe to lead on future connectivity IPR generation, standardization actions while moving higher in the value chain: Leveraging its current strength, Europe can play a leading role in the definition of 6G. Core technologies developed in Europe should also enable to develop more complex connectivity solutions (smart sensors enriched by AI features, more integrated 6G RF solutions, combination of radar and communication, ...) and then capture more value.

#### Mid-term (5 years from now):

- Define an aggressive timeline for the deployment of 6G at the scale of all EU state members: while EU is today playing catch up on 5G deployment, it would be necessary to well anticipate this topic for 6G. Learning from what China did through MIIT's deployment policy, an aggressive agenda for 6G deployment at the scale of all EU member states will greatly boost EU initiatives and secure EU's capability to leverage connectivity infrastructure asset to serve its key verticals.

- Strongly support module integration technologies (both design and fabrication) to combine components from a wide range of technologies (advanced digital and memory chips, but also legacy CMOS, FD-SOI, SOI, BiCMOS, III-V, photonics, sensors): such approach will enable Europe to capture a higher portion of the value chain by delivering systems instead of components. Moreover, it may also allow viable solutions in markets that are not big enough to support the high development cost required by the smallest CMOS nodes. Instead, functionality could be implemented with multiple modularly designed chips in legacy technologies. This can enable defense industry to produce entirely in Europe exploring available production technologies even leadingedge nodes are not available.

- Strengthen the European position on EDA, IP & software: Creating an open and more diverse ecosystem is key to ensure a resilient supply chain and enable Europe to mitigate sovereignty risks. Chip design, a field where USA leads, is expected to play a progressively larger role in driving performance improvements as transistor shrinkage slows.

- Enable smartly positioned European fabless ecosystem: To play a role in advanced computing chips (or modules) and to mitigate Europe's current dependency, a strong European fabless ecosystem is a mandatory starting point.

#### Long term (10 to 15 years from now):

- Make Europe the IC design champion: Europe must become the global IC design champion to ensure its position in connectivity system manufacturing and strong vertical sectors (application industry and domain knowledge as input for chip design) and to preserve their claimed value chain share.

- Enable the establishment of < 2 nm CMOS manufacturing in Europe to support the created domestic market. This can be implemented much sooner through partnerships with strong non-European players.

## 4. First draft of strategic industry-relevant R&I roadmaps

Based on initially identified COREnect end-to-end system view together with value chain consideration, COREnect organizes three COREnect Expert Groups to address the industry roadmaps in three strategic focus areas:

- Expert Group #1 Compute and Store

- Expert Group #2 Connect and Communicate

- Expert Group #3 Sense and Power

Today, the expert groups consist of 96 experts from industry, SME's, research institute, universities, and associations. 61 experts are consortium members, and 35 experts are from outside the consortium. COREnect continuously seeks to optimize the expert group's composition via open calls (https://www.corenect.eu/news/call-for-experts) to obtain an optimal scientific, organizational, and societal balance. For each expert group, a Chair and Vice-Chair have been selected by the COREnect consortium with the responsibility to coordinate

these groups. As a result of several public workshops and focused meetings and brainstorm discussions, the experts aligned their views on Europe's major challenges and opportunities. Combining their specialist knowledge, COREnect benefits from broad insights into crucial fields that require our attention and, thus, address the upcoming challenges in Europe regarding 5G and beyond. Altogether, capturing and crystallizing the discussions, the three expert groups are cooperatively developing the COREnect industry roadmap.

Although each Expert Group is focusing on a defined strategic area, one can find many overlapping topics within this holistic approach. Security and energy efficiency are cross-cutting design considerations in the COREnect technical vision and inherently the common work of Expert Groups. Therefore, the sphere of *Energy Efficient, Green Communication Electronics* will be equally covered in the chapters dedicated to the expert groups. Therein, advanced computation and sustainable fabrication are going to be examined from the perspective of the device itself (EG1), the transceivers (EG2), as well as from the sensors and power management (EG3) point of view.

Regarding 5G/6G application areas, security and trustworthiness are both a focus for several stakeholders. Therefore, technologies to cope with untrusted third-party IP (EG1), telecommunication hardware and software (EG2) and failure detection and security technologies (EG3) are contributing to the question of how to derive *Electronics for Trustworthy Communication* in 6G and beyond. Regarding the technical aspects of the European sovereignty and its ecosystem, the key question is whether a whole European value chain including the tools and knowledge is feasible, required, and how it can be realized.

An integrated approach of *Future Core-Technologies and Integration* throughout all three expert group chapters is going to highlight the areas in packaging, materials, semiconductor, production, and assembly that can bring Europe forward towards a more inclusive and carbonneutral society. For instance, multi-chip modules (MCM) and the integration of memory chiplets (EG1), semiconductor trade-offs for wireless and wireline transceivers (EG2), or heterogeneous integration and the semiconductor processing technology landscape (EG3) and its opportunities for Europe are being reflected on in each chapter. Social inclusion with new user interfaces, knowledge, education and job generation, and the general orientation towards megatrends (e.g., demographic change, global warming) will equally play a role, guiding the proposed strategies towards a common goal.

The specific objectives of the Expert Groups *Compute and Store* (EG1), *Connect and Communicate* (EG2), as well as *Sense and Power* (EG3) are described in the following subsections, along with the initially identified gaps and challenges. The key envisioned strategic actions of the individual expert groups and well as across the expert groups are given in Table 2, Table 3, and Table 4. Each table refers to a time perspective as described in section 3.3, i.e., short-, mid- and long-term. Note that these tables are not complete. They will be revised and consolidated over the upcoming deliverables D3.4 and D3.5

Table 2: Envisioned strategic actions on a short term for EG1, EG2, EG3 and across the expert groups.

| Short term (upcoming 2 years)                                                             |                                                            |                                                         |  |  |  |  |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|

| Strengthen areas where Europe is leading                                                  | Secure access to < 7 nm CMOS technology                    | Strengthen the education on IC design                   |  |  |  |  |

| RAN: broad rollout of 5G over the whole EU                                                | Strengthen Europe on semiconductor manufacturing equipment | RAN: ensure enough IC design<br>engineers are available |  |  |  |  |

| Consumer: focus on RF FEM market                                                          | Foster digitization of European industries                 | Increase collaboration between<br>European entities     |  |  |  |  |

| Consumer: RF Filtering (moved from RAN)                                                   |                                                            |                                                         |  |  |  |  |

| Industrial: support the migration of EU 200 mm fabs to 300 mm                             |                                                            |                                                         |  |  |  |  |

| Support EU microkernel OS research                                                        |                                                            |                                                         |  |  |  |  |

| Develop an MPSoC meta-level<br>description standard for integration of<br>third-party IPs |                                                            |                                                         |  |  |  |  |

Table 3: Envisioned strategic actions on a medium term for EG1, EG2, EG3 and across the expert groups.

| Mid-term (upcoming 5 years)                                   |                                                                                   |                                                                                |  |  |  |  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|

| Enable Europe to lead on future                               | Strengthen European position on EDA,                                              | Enable smartly positioned European                                             |  |  |  |  |

| connectivity standards                                        | IP & software                                                                     | fabless ecosystem                                                              |  |  |  |  |

| RAN: RF-GaN                                                   | Datacenters: extend EU IP portfolio<br>(beyond ARM) to new class of IPs<br>(ADC,) | RAN: digitization of transceiver                                               |  |  |  |  |

| RAN: mmW beamforming transceiver                              | x-EG: Strengthen Europe position on<br>EDA solution market                        | Consumer: mmW transceiver design                                               |  |  |  |  |

| RAN: RF-GaN mmW                                               | Develop a modular secure operating system framework                               | Datacenters: enable low power CPU/GPU design house in EU (using ARM or RISC-V) |  |  |  |  |

| RAN: D Band transceiver                                       |                                                                                   | Strategic Infrastructure program                                               |  |  |  |  |

| Consumer: RF filtering at mmW                                 |                                                                                   | 2.5 and 3D packaging                                                           |  |  |  |  |

| Datacenters: enable EU optical module makers                  |                                                                                   | Low power eNVM for Al                                                          |  |  |  |  |

| Support Europe contribution to standardization activities     |                                                                                   |                                                                                |  |  |  |  |

| Strategic Infrastructure program<br>Radio interface standards |                                                                                   |                                                                                |  |  |  |  |

Table 4: Envisioned strategic actions on a long term for EG1, EG2, EG3 and across the expert groups.

|                                                       | Long-term (10 to 15 years from now)           |  |  |  |  |  |

|-------------------------------------------------------|-----------------------------------------------|--|--|--|--|--|

| Make Europe the IC design champions                   | Enable < 7 nm CMOS manufacturing in<br>Europe |  |  |  |  |  |

| RAN: IEEE 802.15.3D transceivers                      |                                               |  |  |  |  |  |

| Consumer: module for D band communication             |                                               |  |  |  |  |  |

| Consumer: radar functionality with D band transceiver |                                               |  |  |  |  |  |

| Consumer: Low data rate wireless devices              |                                               |  |  |  |  |  |

#### EG1: compute and store

#### 4.1.1. Introduction

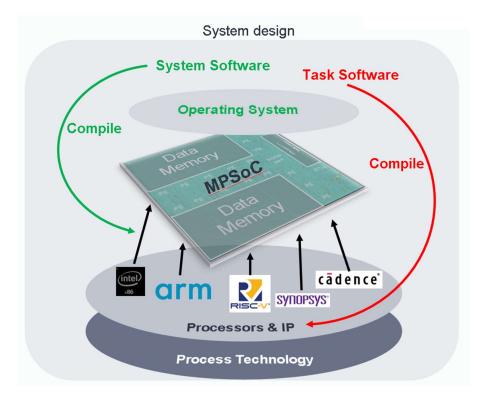

Figure 12: Common architecture of computing systems.

For 5G and beyond, ever more performant digital computing platforms and components will be required. However, Europe is becoming increasingly dependent on non-European supply for these components and systems. This makes the European supply chain highly susceptible to disruptions such as trade wars. Expert Group 1 (EG1) therefore investigates the role of computing and storage solutions for Europe's 5G and 6G sovereignty.

EG1 identifies key technologies that enable Europe to build trustworthy and competitive systems for communication (terminals and the RAN) and different applications (IoT, personal devices and personal mobile robotics). The focus will be on programmable computing platforms and the included storage components under the consideration of different operating constraints and the need to support legacy software.

In section 4.1.2, we will begin with a description of the system requirements for the RAN and the UE (User Equipment) use cases. From these requirements we derive the form needed to fulfill the specific functions at each layer of the computing platform from the bottom-up in this whole chapter (c.f. Figure 12). At the bottom there are the process technologies that are used for physical realization. Section 4.1.3. states some initial thoughts on the requirements which were left out in previous statements of EG1. Modern computing platforms contain at least one, more often multiple, cores whose software interface is defined by the instruction set architecture (ISA). For different situations, such as infrastructure equipment or edge devices, different ISAs may be used, as elaborated in section 4.1.4. The next section, section 4.1.5, analyzes the European position in memory and storage and how it can be improved. The

challenge of integrating multiple heterogenous cores, memories, accelerators (c.f. EG3) and intellectual property (IP) blocks in a Multiprocessor system on a chip (MPSOC) is portrayed in section 4.1.6. Finally, section 4.1.7 proposes an operating system framework which is based on the principles of modularity and microkernel architecture.

#### 4.1.2. 5G/6G System architecture

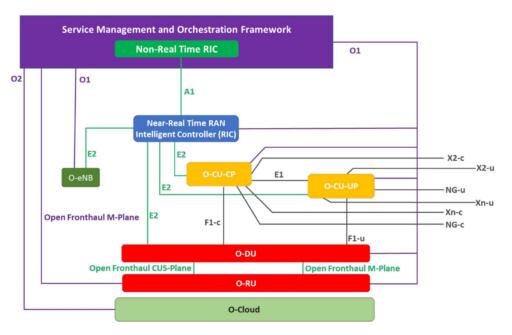

The 5G/6G System Architecture is discussed in two parts: first the Radio Access Network (RAN) and next the User Equipment (UE). Figure 13 shows a logical architecture of the RAN. It is a refinement of Fig. 6.1-1 of 3GPP TS 38.401. The additional interfaces (in green) are specific to the O-RAN Alliance proposal but can also be proprietary.

Figure 13: O-RAN overall logic architecture [ORA19].

#### 4.1.2.1. RAN workload

Most of the RAN compute load is in the radio (RU), central (CU) and distributed units (DU), where (most of) the L1-L3 signal processing occurs. This workload:

- addresses multiple standards, including (3G), 4G, and 5G;

- is complex, highly dynamic, and involves a large number and large variety of different tasks;

- is measured in Peta-ops/sec;

- has to meet extreme latency constraints, measured in micro-seconds per task;

- must support so-called macro network blocks, including their activation and termination.

In addition, some application functions may migrate in part to the base stations (close to the O-CU and final IoT edge AI devices).

#### 4.1.2.2. RAN compute platform

The compute platform likely is to comprise multiple System-on-Chips (SoC). These SoCs are realized in advanced CMOS, possibly including new nanoelectronics technologies such as MRAM, and are connected using novel packaging and interconnect technologies.

- Each SoC includes multiple (100s), diverse compute cores. The HW architecture is heterogeneous.

- Cost pressure and the need for software upgrades will push for programmable ISAbased cores, whereas power constraints will dictate a significant degree of specialization, using a variety of specialized accelerators.

- These cores must be real-time capable to support their dynamic allocation on µsec-msec time scales. Only then can today's massive over-provisioning of hardware resources be avoided.

- The memory organization will be a key challenge: the need for low cost and high flexibility will push for memory unification and centralization, whereas the need for low power will push for memory specialization and distribution.

- The mix of cores and the memory organization must be such that the overall multi-MPSoC RAN can be scaled over a range of workload sizes.

- Also, new system architecture design and thermal-aware and energy-aware optimization methodologies need to be created to enable trade-offs between security, power and performance for the 5G/6G context.

#### 4.1.2.3. RAN run-time mapping

Running the complex, highly dynamic petaflops workload on such a multi-SoC RAN computing platform efficiently is exceptionally challenging. It involves:

- Dynamic, real-time multi-tasking. Virtualization is an ultimate form of this, and it is seen as the holy grail.

- Adaptive resource management, meeting power and thermal constraints during operation.

#### 4.1.2.4. UE

On the UE side, the main challenges arise from the huge diversity in 5G/6G modem requirements, from primitive IoT devices to high-end smartphones. This diversity is about:

- the range of standards (4G, 5G, Wi-Fi, Bluetooth, GPS, NFC, Ethernet...) to be supported,

- the ranges of required bitrates (kbps Gbps), and latency requirements.

Accordingly, the main architectural challenge is building a scalable modem (as IP block, incl. HW/FW/SW), addressing multiple market segments?

Additional UE architecture challenges include:

- support of beamforming, including distributed (coordinated) beamforming by multiple IoT devices;

- additional flexibility on MPSoC to enable ISA extensions and use programmable or reconfigurable (coarse-grained or fine-grained) accelerators;

- adaptive resource management approaches at system level, including power and thermal constraints at run-time during operation;

- potential definition of dynamic, and real-time multi-tasking and architectural flexibility, where virtualization can be an ultimate form of such a flexibility.

#### 4.1.3. Process technology

The future perspective of programmable computing platforms (PCP) for communications dictates the availability of semiconductor technologies with very specific characteristics. Due to, in many cases, contrary requirements of the components in such PCPs, we can already see today that those computing platforms will consist of components based on application-optimized

technologies. Within the digital domain, following criteria will dominate, based on PCP requirements:

- data rate → computational performance at low power

- o leading edge (7 nm-5 nm-3 nm)

- o thermally optimized 2.3D / 3D packaging technology

- real-time → latency → specialized hardware-based AI accelerators

- o low-power technologies for AI on value added technologies

- o low-power embedded Non-Volatile Memory (eNVM)

- cost → cost efficient and reliable 3D packaging technology for system-in-package

- trust → hardware (technology) based secure components (PUFs, secure NVM, etc.)

- bandwidth → RF semiconductor technologies with peak frequencies above 600 GHz

## Logic/Foundry Process Roadmaps (for Volume Production)

|                 | 2016  | 2017 20                     | 18                 | 2019                     | 2020                 | 2021                        | 2022                  |

|-----------------|-------|-----------------------------|--------------------|--------------------------|----------------------|-----------------------------|-----------------------|

| Intel           | 14nm+ | 10nm<br>(limited)<br>14nm++ |                    | 10nm                     | 10nm+                | 10nm++                      | 7nm<br>EUV            |

| Samsung         | 10nm  |                             | 8nm                | 7nm<br>EUV<br>6nm<br>EUV | 18nm<br>FDSOI<br>5nm | 4nm                         | 3nm<br>GAA            |

| TSMC            | 10nm  | 7nm<br>12nm                 |                    | 7nm+<br>EUV              | 5nm<br>6nm           | 5nm+                        | 4nm<br>3nm            |

| GlobalFoundries |       | 22nr<br>FDSO                | n 12nm<br>I finFET | · ·                      | 12nm<br>FDSOI F      | nm+<br>DSOI 12nm+<br>finFET |                       |

| SMIC            |       |                             |                    | 14nm<br>finFET           | 12nm<br>finFET       |                             | 0nm<br><sub>FET</sub> |

| имс             |       | 14nm<br>finFET              |                    |                          | 22nm<br>planar       |                             |                       |

Note: What defines a process "generation" and the start of "volume" production varies from company to company, and may be influenced by marketing embelishments, so these points of transition should only be seen as very general guidelines.

Sources: Companies, conference reports, IC Insights

Figure 14: Leading Edge foundry process roadmap [ICI21].

Moore's Law has always been about power, performance and cost. Continuously increasing amount of data being transferred and processed will require system components in a PCP which are built based on leading-edge digital technologies ("7 nm", "5 nm" down to "2 nm"). Only these technologies will be capable to resolve the trade-off between computational performance and power requirements (and cost). Figure 14 shows an overview of the logic/foundry process roadmaps as distributed by [ICI21].

It should be noted that Figure 14 depicts the leading-edge offerings only. Integration of NVM, analog, power and RF into CMOS-technologies can only be done on legacy technologies. This aspect is of high importance, as significant reductions in power, construction size and cost can only be achieved with value-added integration.

In addition to technology advancements, significant reductions in power consumption can be achieved using specialized AI components performing dedicated tasks within a PCP. These AI

accelerators not only contribute to the real-time capability of the entire system. Properly designed and using Al-optimized technology components, like low-power analogue calculators and low-power embedded NVM, these Al accelerators significantly reduce system power consumption. Neither the Al functions, nor the eNVM components require the most advanced technologies, but would like to use the functional integration of value-added technologies. Moreover, eNVM can only be offered in rather mature technologies, which are also available through European semiconductor manufacturers. So, the focus here must be placed more on the architecture and design of such Al components and the usage on trusted technologies from Europe in view to achieve increased sovereignty. In addition, the number of specialized Al accelerators in the PCP should be increased to a possible maximum to save as much power as possible.

Replacing generic Al-accelerators with dedicated Al-accelerators on processes with high integration value, trustworthy and secure provision from Europe, will position us well for the future in the context of 6G.

Due to numerous functional components in a future PCP, special focus must be put on the system integration. 2.5D and 3D packaging technology is being extensively used to reduce parasitic limitations (I/O loadings) and thus increase system efficiency to both, power consumption and data throughput. On top, appropriate packaging technologies are capable to combine trusted components (AI, eNVM, RF) with those originating from untrusted manufacturing sources (digital "7 nm", "5 nm" down to "2 nm"). Using appropriate components providing trust, untrusted system components can be used and "upgraded" to the required trust level.

Unfortunately, standard packaging technologies are not very well represented in the European technology landscape. However, there is the opportunity to gain a lead in advanced 2.5 & 3D integration. Special focus will have to be placed on thermal aspects and we will have to divert some of the gains of Moore's law from "performance" to "lowering power", more than we have done in the past.

Controlling 3D-Integration will provide us with a lead in designing security solutions and build trusted systems out of Europe independently.

#### 4.1.4. Instruction set architecture (ISA)

The Instruction Set Architecture (ISA) and its realization as a microarchitecture can be an enabling factor for innovation as described in D3.1. In the context of 5G/6G applications, we need to consider solutions covering IoT and edge devices as well as infrastructure equipment. For infrastructure equipment standard ISAs provide a good solution, while for small IoT and edge devices more application-specific solutions based on non-standard ISAs/DSLs are needed. For both scenarios also, solutions based on application-specific adaptations of standard ISAs, such as RISC-V which is an open-source initiative for core processor architecture design, play an important role. We identified the following open challenges and topics for each of them.

Standard ISA for infrastructure equipment:

High Performance Chip Design: High performance implementations in silicon are very challenging and require highly skilled CPU architects/designers (and possibly custom design at the gate level), which is currently a scare resource in Europe.

- Dynamic Binary Translation (DBT): Another road to high-performance ISA implementation is using DBT to a simpler core, as done by NVIDIA with the Denver/Denver2 cores implementing ARMv8 ISA and by Apple with the Rosetta DBT. An extended RISC-V implementation could be the target of a DBT, both could possibly be in the EU skillset.

- Adaptations of Standard ISAs (e.g., 64-bit RISC-V): There are a few EU 64-bit RISC-V implementations: The Ariane-based from ETHZ (now on openhwgroup.org/cva6), the NOEL-V from Cobham Gaisler, the Avispado and Atrevido from SemiDynamics. It is not expected that EU-designed RISC-V processors become competitive with high-end X86 or ARMv8 implementations in USA or Asia (China, Japan, Korea) for latency-constrained applications. However, it is expected that these eventual performance limitations of EU RV64G cores will not be a major problem for accelerated computing scenarios at the edge, in particular for 5G/6G applications. On the contrary, the ISA adaptation opportunities of the RISC-V environment will enable more tuning for these accelerated computing scenarios, in particular in the privileged ISA (on the memory models).

- Formal verification of ISA implementations: Whether RISC-V related or not (OneSpin also did it on the Infineon TriCore2, on Bosch DSPs, etc.) are of high importance to ensure trustable and reliable realizations.

Non-standard ISAs / DSLs for edge devices:

- Non-standard ISAs: Can be hidden and easily integrated into the software stack if they

operate beyond a DSL; this is already the case for AI in Multi-access Edge Computing and

could be the case for the L1/L2 RAN processing.

- Acceleration DSLs: May lead to specific/relaxed requirements on the accelerator memory model and the way it is seen from the GPP. Having the accelerator to operate under CAPI, CCIX or CXL may be less important than in datacenters, as latency and energy-efficiency plays a crucial role in the edge.

#### 4.1.5. Memory and Storage